|

The ProjectIn this project, we were tasked with creating a receiver that incorporated a FPGA. This receiver was meant to take information coded in a wave, using a modulation technique of our choosing, and retrieve it. The only stipulation for this was that it had to incorporate a FPGA, coded in our choice of Verilog or VHDL, and had to take care of the demodulation aspects of retrieving a signal. We were given several liberties about how exactly how to approach the project, most of which can be found on the specifications page. To the left, you will find links to various aspects of our project, from our design process to the software and hardware we used for this project. Also, keep in mind that this web site only contains a brief summary of our project. For a more complete overview, please download our project report. |

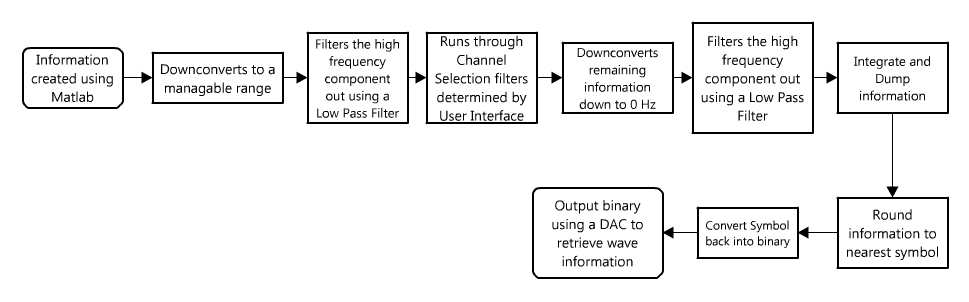

Design OverviewBelow is a picture showing overall design of our product, followed by a list giving more information about each section. Again, more information can be found in our final results paper.

|