Design Process: Phase 3

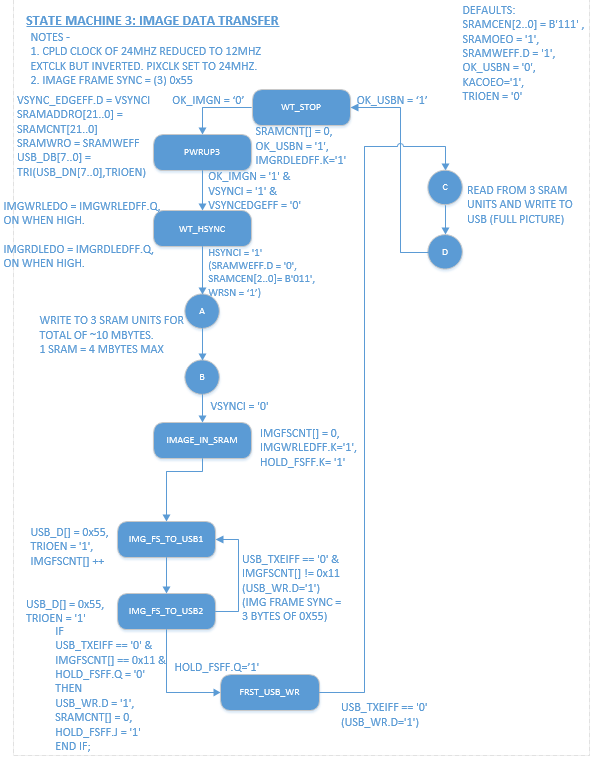

(State Machine Diagram 3)

Key Milestones:

-- State Machine Diagrams - 01/20/2015

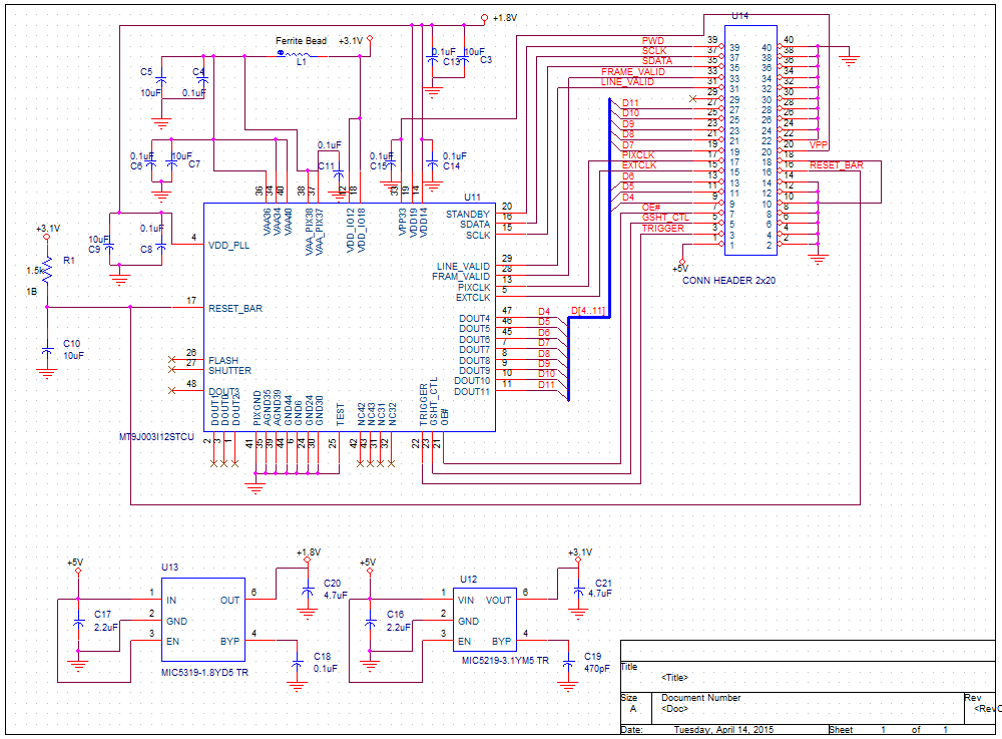

-- Sensor Board Schematic - 02/11/2015

-- Control Board Schematic - 03/03/2015

-- Midterm Client Status Report - 03/08/2015

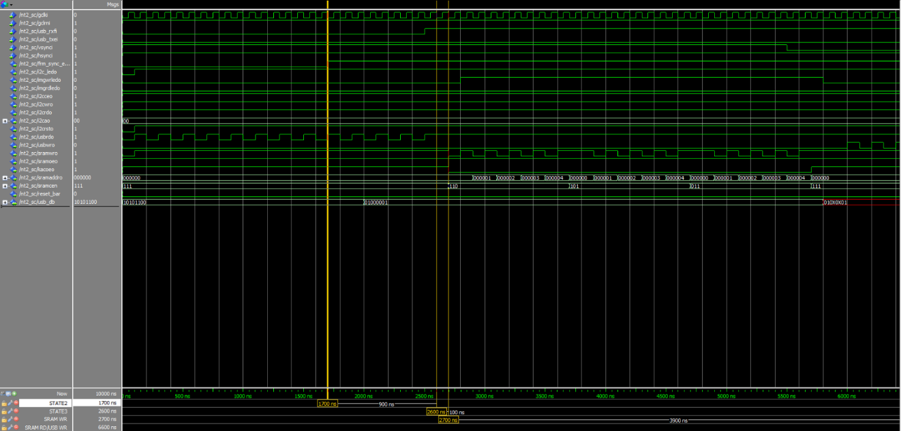

-- CPLD Simulations - 03/19/2015

State Machine Diagrams:

The figure to the left is an example of one of the three state machine diagrams that were created to map the signal behaviours in and out of the CPLD. This was an important first step to fully understand how all the components would communicate with each other.