Final Product

The project has two different aspects, both of which will be delivered to Cobham. This page will go into some of the details of what exactly is being delivered

FPGA/Verilog Code

For the FPGA part of the project, we will be delivering the Xilinx Spartan 6 SP605 FPGA board (which was supplied to the team by Cobham in the first place), along with all of the code the team wrote. The code written in Verilog was the primary aspect of this part of the project. The code that is being delivered accomplishes the desired functionality of being able to communicate with the computer GUI as well as being able to store sent and received data. When given the 'go' signal from the GUI, the FPGA will send the stored information out of one port and receive it on a different port and store this information in a different memory block. When requested, the FPGA will send information back to the computer.

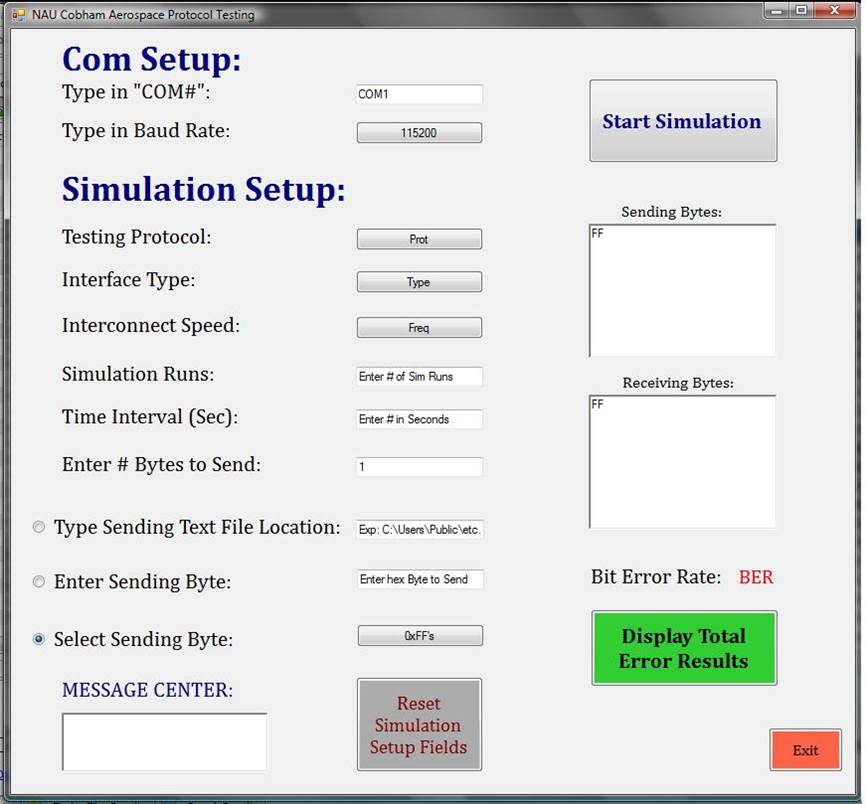

GUI

The GUI being delivered allows the user to control the testing. The current functionality that has been implemented includes choosing the baud rate, the com port to be used to communicate with the FPGA, an enterable number of bytes to be sent (1-256), a selectable list of premade bytes to send, the ability to enter a custom byte to send, a reset button and a start simulation button. The GUI will take the entered information, package it appropriately and send it to the FPGA board. The GUI will then wait for a 'test finished' flag from the FPGA and will then retrieve the information and compare it to the initial bytes sent, allowing for the calculation of the bit error rate.

Entire System

Both pieces, the GUI and the FPGA, work together to test the desired communication protocol. The GUI will send information to the FPGA, which will store it in memory. The FPGA will then wait for a 'go' command from the GUI. Once that command is received, the FPGA will then send the received information out of one port and receive it on another and store this new information in memory as well. The GUI will be looking at a 'done' flag on the FPGA. The FPGA will set this flag once it has finished receiving all of the information. Once the GUI sees the 'done' flag, the GUI will then go through and read all of the information back. At this point, it can calculate the bit error rate by comparing the initial information to the received information